▲

- A TSMC decidiu não utilizar a litografia High-NA EUV no processo de fabricação A14 (1.4nm).

- Essa escolha pode impactar o custo e a competitividade dos chipsets fabricados pela TSMC.

- Com a decisão, a TSMC pode enfrentar desafios de desempenho em comparação com concorrentes que adotam tecnologias mais avançadas.

- A empresa foca na otimização de custos, mas isso pode afetar sua liderança no setor de semicondutores.

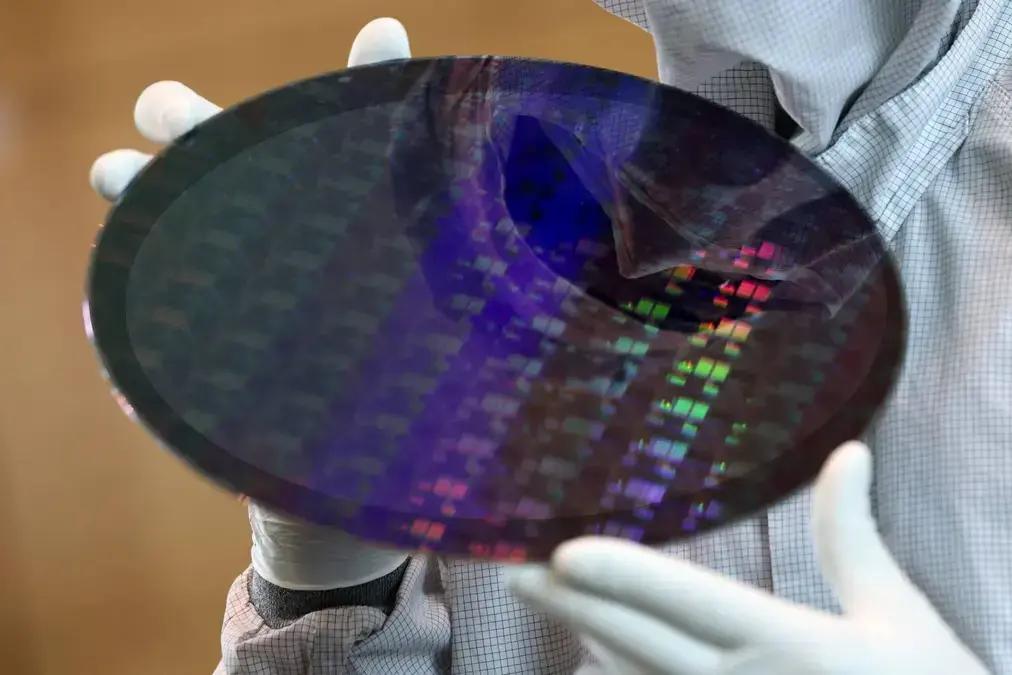

A TSMC High-NA EUV, gigante taiwanesa do setor de semicondutores, parece estar adotando uma postura estratégica em relação à adoção da litografia High-NA EUV. Rumores indicam que a empresa não utilizará essa tecnologia no processo A14 (1.4nm), priorizando a eficiência de custos em vez do desempenho máximo. Essa decisão coloca a TSMC em uma posição diferente de outras empresas, como a Intel Foundry, que já estão investindo na High-NA EUV.

TSMC prioriza custo-benefício em vez de adotar a High-NA EUV para o processo A14 (1.4nm).

Tradicionalmente, a TSMC tem sido pioneira na adoção de novas tecnologias no setor de semicondutores, muitas vezes ditando tendências. No entanto, a empresa parece estar mudando sua abordagem com o processo A14, optando pela tecnologia EUV convencional de 0.33-NA em vez da High-NA EUV. Essa informação foi divulgada por Kevin Zhang, vice-presidente sênior da TSMC, durante o NA Technology Symposium.

Com essa decisão, empresas como a Intel Foundry e diversos fabricantes de DRAM ganham uma vantagem tecnológica sobre a TSMC no que se refere à adoção da High-NA EUV. A TSMC parece estar focada em otimizar os custos de produção, mesmo que isso signifique não utilizar a tecnologia mais avançada disponível.

A decisão de não usar a High-NA EUV na produção dos chips A14, prevista para começar em 2028, mostra que a TSMC busca manter a complexidade de processamento em níveis similares aos atuais, sem aumentar o número de máscaras utilizadas. Essa estratégia é fundamental para garantir uma solução de custo-benefício eficiente.

Leia também:

Estratégia da TSMC para o processo A14

A TSMC busca minimizar o aumento no número de máscaras a cada nova geração de tecnologia, visando oferecer soluções com melhor relação custo-benefício. Essa abordagem pode impactar o desempenho dos chips A14, mas a empresa acredita que a otimização de custos é mais importante nesse momento.

Ainda não está claro como essa decisão afetará a competitividade dos chips da TSMC no longo prazo. A High-NA EUV promete avanços significativos em termos de densidade e desempenho dos chips, e a TSMC pode estar perdendo uma oportunidade de se destacar nesse aspecto.

A recente lei criada em Taiwan para proteger a produção avançada de chips, pode ter influenciado na decisão da TSMC High-NA EUV, visto que manter a tecnologia no país é crucial.

Implicações da Decisão da TSMC

Ao optar por não adotar a High-NA EUV para o processo A14, a TSMC pode estar sinalizando uma mudança em sua estratégia. A empresa pode estar priorizando a estabilidade e a previsibilidade dos custos em vez de buscar o desempenho máximo a qualquer custo.

Essa decisão pode ser vista como uma resposta às crescentes pressões do mercado, que exige soluções cada vez mais eficientes e acessíveis. A TSMC pode estar buscando um equilíbrio entre inovação e viabilidade econômica, garantindo sua posição como líder no setor de semicondutores.

O mercado observa atentamente os próximos passos da TSMC e como essa decisão impactará seus produtos e sua posição no mercado global. A empresa enfrenta o desafio de manter sua relevância em um cenário tecnológico em constante evolução, equilibrando custos e desempenho.

O foco em dados de qualidade e IA pode ser uma estratégia para a TSMC otimizar seus processos e garantir a eficiência de custos em suas operações.

O Futuro da Litografia EUV na TSMC

Apesar de não utilizar a High-NA EUV no processo A14, a TSMC continua investindo em tecnologias de litografia avançadas. A empresa deve receber equipamentos High-NA EUV da ASML até o final deste ano, com um custo estimado de 350 milhões de dólares.

Esses investimentos indicam que a TSMC reconhece o potencial da High-NA EUV e pode vir a adotá-la em processos futuros. A empresa pode estar buscando um período de avaliação e testes antes de implementar a tecnologia em larga escala, garantindo que ela esteja madura e otimizada para suas necessidades.

A decisão de pular a High-NA EUV no processo A14 pode ser uma jogada estratégica da TSMC, visando garantir sua competitividade e rentabilidade no longo prazo. Resta saber como essa estratégia se desenrolará e qual será o impacto no mercado de semicondutores.

Este conteúdo foi auxiliado por Inteligência Artificiado, mas escrito e revisado por um humano.